74HC595引脚图及功能:74HC595工作原理及作用

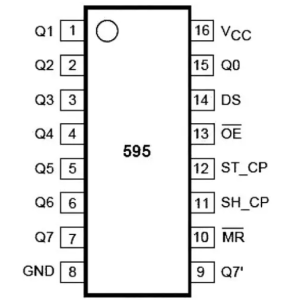

74HC595引脚图及功能

74HC595是一种串/并转换芯片,常用于数字信号处理、计数器、显示屏控制等领域。它的主要引脚和功能如下:

- Qh’(引脚15):串行数据输入;

- Qa~Qh(引脚1~7, 9~14):并行输出;

- SRCLR(引脚10):清空锁存器,将Qa~Qh复位为0;

- OE(引脚13):使能输出使能,允许或禁止并行输出;

- SHCP(引脚11):移位时钟输入,控制串行数据的移位;

- STCP(引脚12):存储器时钟输入,控制锁存器中的数据存储。

需要注意的是,在使用74HC595芯片时,应根据具体的应用场合和性能需求进行选择,并注意其相关的参数和管脚连接方式。此外,在串/并转换的过程中还需要注意时序控制、数据输入输出、电源供应等方面的问题,以确保芯片正常工作。

74HC595工作原理及作用

74HC595是一种串/并转换芯片,可以将串行数据转换为并行数据输出,并且可以连接多个芯片进行级联。其工作原理如下:

- 在移位寄存器时钟SHCP的控制下,串行输入信号从引脚Qh’进入芯片;

- 移位寄存器中的数据在存储寄存器时钟STCP的控制下被锁存,成为并行输出信号Qa~Qh;

- 通过OE使能管脚的控制,可以允许或禁止并行输出;

- 可以通过级联方式扩展到更多芯片,实现更多位数据的并行输出。

74HC595常用于数字信号处理、计数器、显示屏控制等领域,在电子设备中得到广泛应用。其作用主要包括将串行数据转换为并行数据输出,实现高效的数据传输和处理,提高芯片性能和系统可靠性。

综上所述,74HC595是一种常见的串/并转换芯片,在数字信号处理、计数器、显示屏控制等领域得到广泛应用。在选择和应用74HC595芯片时,需要了解其引脚图和功能表,并注意其相关的参数和管脚连接方式,以确保芯片正常工作。同时,在设计电路时还需要注意其工作原理和特点,并进行充分的测试和验证,以确保电路的可靠性和稳定性。