74LS373引脚图及功能真值表

74LS373是一种8位锁存器,采用三态输出,具有输入数据存储、输出数据驱动、数据总线隔离等多种功能,广泛应用于数字逻辑电路中。

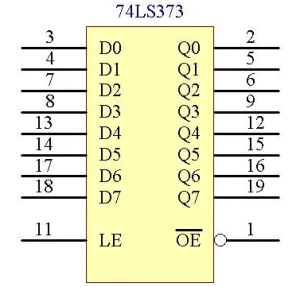

其引脚图如下:

其中,1~8为数据输入端口D0~D7,9为主复位端口MR,10为时钟端口CP,11为输出允许端口OE,12~19为数据输出端口Q0~Q7,20为负电源VCC,21为地GND。

其功能真值表如下:

| CP | D | MR | OE | Q |

|---|---|---|---|---|

| L | X | H | H | Q |

| ↑ | X | X | X | Hold |

| X | L | X | L | 0 |

| X | H | X | L | 1 |

其中,“X”表示输入不确定。当CP为低电平时,输入信号被保持(Hold)在锁存器中,不会反映到输出上。当CP有正跳变(↑)时,锁存器接收到D输入的信息,并通过Q输出进行驱动控制。当OE为低电平时,输出使能,数据将从Q0~Q7输出;反之,当OE为高电平时,输出禁止,数据输出端口处于高阻态。

74LS373功能及使用方法

74LS373锁存器具有广泛的应用场景,例如:

- 并行总线控制:利用锁存器实现数据输入、输出和存储等功能,控制并行总线的通讯;

- 存储器扩展:通过多个锁存器级联,扩展存储器容量,实现大型数字电路的存储与处理;

- 数据缓冲:将数据缓存到锁存器中,提高数据传输速率和稳定性。

在进行74LS373的应用时,需要注意以下几点:

- 电源稳定:保证正负电源电压稳定,以确保电路正常工作;

- 时序设计:根据具体应用需求,合理设计时序及CP脉冲宽度,以兼顾高速和功耗等方面的要求;

- 输出驱动:根据电路负载情况选择适当的输出电流及输出驱动方式,以确保输出信号的稳定性和可靠性。

需要注意的是,在进行电路设计和测试时,应按照器件规格书和相关标准进行操作,并采取相应的保护措施,确保器件和电路的安全和稳定。